Chinmay Mittal

I am a senior Computer Science and Engineering undergrad at IIT Delhi and am broadly interested in Artificial Intelligence and Computer Systems. I’ll be joining Optiver as a Software Engineer next summer where I interned last summer. I’ll be primarily involved in programming trading systems.

I am currently working with Prof. Mausam and Prof. Parag Singla on Neuro-Symbolic approaches for improving the reasoning abilities of Large Language Models, particularly focussed on NP-Hard problems. Previously, I worked with Prof. Chetan Arora and the MAVI group on improving Deep Learning models for Scene Text Recognition of Indic Languages.

I am also the Vice Chair at ACES-ACM, the CS society at IIT Delhi and the student chapter of ACM. We organize engaging events for CS students and make sure CS people have a great time at IITD.

I interned with the architecture group at Yale University where I worked on Machine Learning models for Brain Computing Interfaces. During my internship at Tower Research, I worked on Machine Learning techniques for quantitative finance. I also interned at Fractal AI where I worked on a dynamic demand forecasting engine.

I also really like teaching and writing. I am a Teaching Assistant for the Introductory Course on Artificial Intelligence on NPTEL by Prof. Mausam. I was a Teaching Assistant for COL100, the introductory course for Computer Science and programming at IIT Delhi. I sometimes write technical content on Medium and LinkedIn. I also enjoy music, football and gymming.

For more detailed information please check out my resume 📃

Projects & Programming Explorations

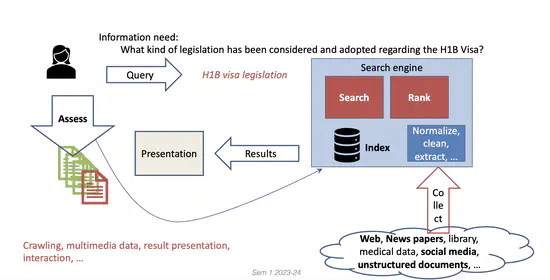

COVID-19 Search Engine

An inverted index based search engine in C++ for COVID-19 related news and research

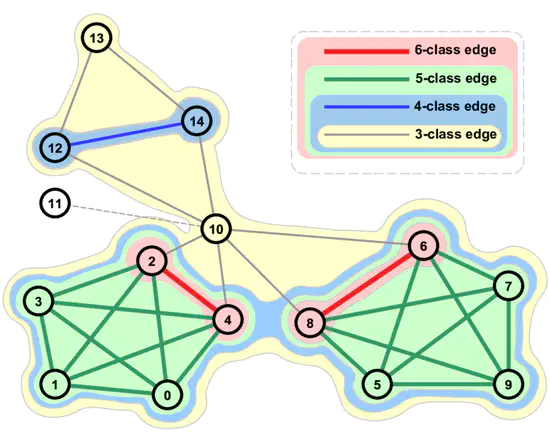

Speed-Truss

A parallel and distributed program for super-fast K-Truss decomposition of extremely large and dense graphs

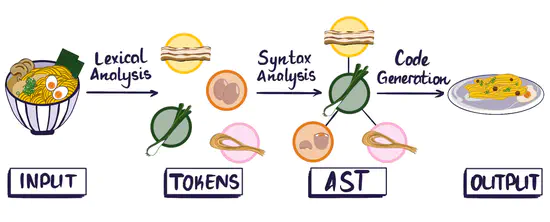

Compiler for a simplistic C-syntaxed programming Language

A simplistic compiler for the hypotheical WHILE programming language in SML